# INTEGRATED CIRCUIT PACKAGING, ASSEMBLY AND INTERCONNECTIONS

# INTEGRATED CIRCUIT PACKAGING, ASSEMBLY AND INTERCONNECTIONS

William J. Greig Consultant Somerville, New Jersey, USA

William J. Greig Consultant 10 Imperial Drive Somerville, NJ 08876

Integrated Circuit Packaging, Assembly and Interconnections

Library of Congress Control Number: 2006927423

| ISBN 0-387-28153-3    | e-ISBN 0-387-33913-2    |

|-----------------------|-------------------------|

| ISBN 978-0387-28153-7 | e-ISBN 978-0387-33913-9 |

Printed on acid-free paper.

© 2007 Springer Science+Business Media LLC

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks and similar terms, even if the are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

987654321

springer.com

## **DEDICATION**

To my family,

my wife Joan

and

our children, their spouses and grandchildren

Karen – Christopher, Ryan, Kevin Billy and Cathy – Alli, Jeff, Shauna Joni and Fred – Danny, Kerri, Traci Jo Jimmy and Colleen – Maggie, Molly, Katie, Claire Ronny and Meryl – RJ, Connor Steven Kenny

# **Table of Contents**

| List of Figures  | xiii  |

|------------------|-------|

| List of Tables   | xxi   |

| Preface          | xxiii |

| Acknowledgements | XXV   |

| About the Author | xxvii |

## 1 Electronic Manufacturing and the Integrated Circuit......1

| 1 — MICROELECTRONICS AND THE TRANSISTOR                    | 1 |

|------------------------------------------------------------|---|

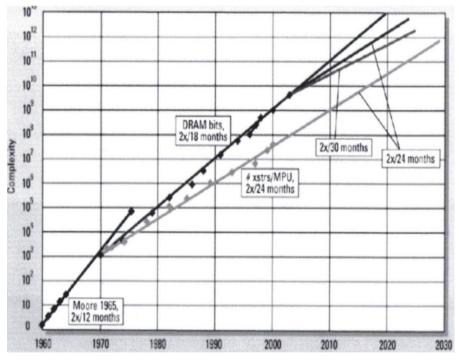

| 1.1 — The Integrated Circuit and Moore's Law (2-5)         |   |

| 1.2 — Electronics Manufacturing and the Technology Drivers |   |

| 1.3 — A Technology Driver—The Integrated Circuit           |   |

| 1.4 — The International Roadmap for Semiconductors (ITRS)  |   |

|                                                            |   |

## 2 Integrated Circuit Manufacturing: A Technology Resource... 15

| 2 — IC MANUFACTURING TECHNOLOGIES                                | 15 |

|------------------------------------------------------------------|----|

| 2.1 — Overview of the IC Manufacturing Processes                 |    |

| 2.2 — The Manufacturing Environment                              |    |

| 2.3 — The Photolithographic Process                              |    |

| 2.4 — IC Methodologies and Packaging, Assembly, Interconnections |    |

##

| 3 — THE IC PACKAGE                 |  |

|------------------------------------|--|

| 3.1 — Trends in IC Packaging       |  |

| 3.2 — Area Array Packages—PGA, BGA |  |

| 3.3 — BGA Surface Mount Assembly   |  |

| 3.4 — BGA Attributes               |  |

| 3.5 — BGA Concerns                 |  |

| 3.6 — The Future                   |  |

| 3.7 — Lead-Free Manufacturing      |  |

| vii | in Integrated Circuit Packaging, Assembly and Interconnections      |      |

|-----|---------------------------------------------------------------------|------|

| 4   | The Chip Scale Package                                              | 47   |

|     | 4 — THE CHIP SCALE PACKAGE, CSP                                     | 47   |

|     | 4.1 — Chip Scale Package Manufacturing Technologies                 |      |

|     | $4.2 - \text{The } \mu \text{BGA}^{\text{TM}}$                      | 52   |

|     | 4.3 — Wafer Level Packaging—The WLP                                 | 55   |

|     | 4.4 — Reliability Concerns                                          | 57   |

|     | 4.5 — Summary                                                       |      |

| 5   | Multichip Packaging                                                 | 61   |

|     | 5 — MULTICHIP PACKAGING (MCP)                                       | 61   |

|     | 5.1 — MCP Substrate/Package Technologies                            |      |

|     | 5.2 — The Hybrid Circuit                                            | 62   |

|     | 5.3 — The Multichip Module (MCM)                                    | 65   |

|     | 5.4 — 3-D Packaging                                                 |      |

|     | 5.5 — 3-D Packaging and the Flex Circuit                            |      |

|     | 5.6 — Die Stacking Using Silicon Thru-Vias                          | 75   |

|     | 5.7 — System in Package (SiP)/System on Package (SoP)               |      |

|     | 5.8 — Summary—Benefits of Multichip Packaging                       | 79   |

| 6   | Known Good Die (KGD)                                                | 81   |

|     | 6 — THE KGD STORY                                                   |      |

|     | 6.1 — The Semiconductor Assembly/Packaging/Test Process             |      |

|     | 6.2 — The Bare Die Problem                                          |      |

|     | 6.3 — Addressing the Bare Die Problem—Wafer Lot Acceptance Testing. |      |

|     | 6.4 — Known Good Die (KGD)                                          |      |

|     | 6.5 — Wafer Level Burn-in and Test (WLBT)                           |      |

|     | 6.6 — Industry Responsiveness                                       | 92   |

| 7   | Packaging Options—Chip on Board                                     | 93   |

|     | 7 — DIRECT CHIP ATTACH (DCA) AND CHIP ON BOARD (COB)                | 93   |

|     | 7.1 — The COB Process                                               | 94   |

|     | 7.2 — Flip Chip On Board (FCOB)                                     | 98   |

|     | 7.3 — Summary                                                       | .101 |

| 8   | Chip & Wire Assembly                                                | 103  |

|     | 8 — CHIP & WIRE ASSEMBLY                                            | .103 |

|     | 8.1 — Die/Wire Bonding and Bonder Equipment Development             |      |

|     | 8.2 — Impact of the IC on Bonding and Bonder Development            |      |

|     | 8.3 — The Chip and Wire Assembly Process                            |      |

|    | 8.4 — Bonding Wire: Au, Al, and Cu                                                 | 106                                                                                            |

|----|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|    | 8.5 — Bonding Methods                                                              |                                                                                                |

|    | 8.6 — Types of Bonds                                                               | 110                                                                                            |

|    | 8.7 — The Ball Bonding Process                                                     | 110                                                                                            |

|    | 8.7 - 11c Dati Doliulig 110cess                                                    | 110                                                                                            |

|    | 8.8 — Wedge Bonding.                                                               |                                                                                                |

|    | 8.9 — Obstacles to Quality and Reliable Wire Bonding                               |                                                                                                |

|    | 8.10 — Metallurgical Concerns and Surface Finishes                                 | 114                                                                                            |

|    | 8.11 — Handling and Storage                                                        | 118                                                                                            |

|    | 8.12 — Verifying Wire Bonding Quality                                              |                                                                                                |

|    | 8.13 — Responding to the IC and End Product                                        |                                                                                                |

|    | 8.14 — Wire Bonding on Organic Substrates, The PBGA and PWB                        | 125                                                                                            |

|    | 8.14 — whe boliding on Organic Substrates, the r DOA and r w D                     | 127                                                                                            |

|    | 8.15 — Summary                                                                     | 127                                                                                            |

|    |                                                                                    |                                                                                                |

| 0  | Tono Automated Danding TAD                                                         | 120                                                                                            |

| 9  | Tape Automated Bonding—TAB                                                         | . 149                                                                                          |

|    |                                                                                    |                                                                                                |

| 9  | - BACKGROUND-MINIMOD                                                               | 129                                                                                            |

|    | 9.1 — Tape Automated Bonding                                                       | 129                                                                                            |

|    | 9.2 — The TAB Tape                                                                 | 129                                                                                            |

|    | 9.3 — TAB Assembly                                                                 |                                                                                                |

|    | 9.4 — Reliability Concerns                                                         |                                                                                                |

|    | 9.5 — Areas of Applications                                                        |                                                                                                |

|    |                                                                                    |                                                                                                |

|    | 9.6 — Summary                                                                      | 140                                                                                            |

|    |                                                                                    |                                                                                                |

|    |                                                                                    |                                                                                                |

| 10 | Flin Chin The Pumping Processes                                                    | 1/2                                                                                            |

| 10 | Flip Chip—The Bumping Processes                                                    | . 143                                                                                          |

|    |                                                                                    |                                                                                                |

|    | 0 — BACKGROUND                                                                     | 143                                                                                            |

|    |                                                                                    | 143                                                                                            |

|    | <b>0 — BACKGROUND</b><br>10.1 — IBM's Flip Chip Transistor<br>10.2 — Wafer Bumping | <b>143</b><br>143                                                                              |

|    | <b>0 — BACKGROUND</b><br>10.1 — IBM's Flip Chip Transistor<br>10.2 — Wafer Bumping | <b>143</b><br>143                                                                              |

|    | <ul> <li><b>0</b> — BACKGROUND</li></ul>                                           | <b>143</b><br>143<br>147<br>150                                                                |

|    | <ul> <li><b>0</b> — BACKGROUND</li></ul>                                           | 143<br>143<br>147<br>150<br>160                                                                |

|    | <ul> <li><b>0</b> — BACKGROUND</li></ul>                                           | 143<br>143<br>147<br>150<br>160<br>161                                                         |

|    | <ul> <li><b>0</b>— BACKGROUND</li></ul>                                            | 143<br>143<br>147<br>150<br>160<br>161<br>163                                                  |

|    | <ul> <li><b>0</b> — BACKGROUND</li></ul>                                           | 143<br>143<br>147<br>150<br>160<br>161<br>163                                                  |

|    | <ul> <li><b>0</b>— BACKGROUND</li></ul>                                            | 143<br>143<br>147<br>150<br>160<br>161<br>163                                                  |

| 1  | <ul> <li><b>0</b> — BACKGROUND</li></ul>                                           | 143<br>143<br>147<br>150<br>160<br>161<br>163<br>165                                           |

| 1  | <ul> <li><b>0</b>— BACKGROUND</li></ul>                                            | 143<br>143<br>147<br>150<br>160<br>161<br>163<br>165                                           |

| 1  | <ul> <li><b>0</b>— BACKGROUND</li></ul>                                            | 143<br>143<br>147<br>150<br>160<br>163<br>163<br>165                                           |

| 1  | <ul> <li><b>0</b> — BACKGROUND</li></ul>                                           | 143<br>143<br>147<br>150<br>160<br>163<br>165<br>169<br>169                                    |

| 1  | <ul> <li><b>0</b> — BACKGROUND</li></ul>                                           | 143<br>147<br>150<br>160<br>161<br>163<br>165<br>169<br>169<br>170                             |

| 1  | <ul> <li><b>0</b> — BACKGROUND</li></ul>                                           | 143<br>143<br>147<br>150<br>160<br>161<br>165<br>169<br>169<br>170<br>171                      |

| 1  | <ul> <li><b>0</b> — BACKGROUND</li></ul>                                           | 143<br>143<br>147<br>150<br>160<br>161<br>165<br>169<br>169<br>170<br>171                      |

| 1  | <ul> <li><b>0</b> — BACKGROUND</li></ul>                                           | 143<br>143<br>147<br>150<br>160<br>161<br>165<br>169<br>169<br>170<br>171                      |

| 1  | <ul> <li><b>0</b>— BACKGROUND</li></ul>                                            | 143<br>143<br>147<br>150<br>160<br>161<br>163<br>165<br>169<br>169<br>170<br>171<br>173<br>182 |

| 1  | <ul> <li><b>0</b>— BACKGROUND</li></ul>                                            | 143<br>143<br>147<br>150<br>160<br>161<br>163<br>165<br>169<br>170<br>171<br>173<br>182<br>183 |

| 1  | <ul> <li><b>0</b>— BACKGROUND</li></ul>                                            | 143<br>147<br>150<br>160<br>161<br>163<br>165<br>169<br>170<br>171<br>173<br>182<br>183<br>183 |

| Х  | Integrated Circuit Packaging, Assembly and Interconnections           |      |

|----|-----------------------------------------------------------------------|------|

|    | 11.8 — Adhesive Bumps                                                 |      |

|    | 11.9 — Summary: Advantages of Flip Chip as a First Level Interconnect | t189 |

| 12 | 8 8                                                                   |      |

|    | Technology                                                            | 193  |

| 1  | 12 — HIGH DENSITY PACKAGE/SUBSTRATE MANUFACTURING<br>TECHNOLOGIES     |      |

|    | 12.1 — Thin Film Technology                                           |      |

|    | 12.2 — The Patterning Process                                         |      |

|    | 12.3 — Processing an HDI Substrate Interconnect                       |      |

|    | 12.4 — Thin Film Materials                                            |      |

|    | 12.5 — Alternative Thin Film Processes for MCP Applications           |      |

|    | 12.6 — High Density Interconnects—Cost and Yield Considerations       |      |

|    |                                                                       |      |

| 13 | HDI Substrate Manufacturing Technologies: Thick Film                  |      |

|    | Technology                                                            | 221  |

|    | 87                                                                    |      |

| 1  | 13 — THICK FILM TECHNOLOGY                                            |      |

|    | 13.1 — The Thick Film Process                                         |      |

|    | 13.2 — The Patterning Process                                         | 222  |

|    | 13.3 — Thick Film Screen Printing and MCM-C/HDI                       | 227  |

|    | 13.4 — Advanced Thick Film Patterning Processes                       | 229  |

| 14 | HDI Substrate Manufacturing Technologies: Cofired                     |      |

| 17 | Ceramic                                                               | 233  |

|    |                                                                       | 200  |

| 1  | 4 — THE COFIRED CERAMIC TAPE TECHNOLOGY                               | 233  |

|    | 14.1 — IBM's Multilayer Interconnect (MLI) Packaging Program          | 234  |

|    | 14.2 — The Co-fired Ceramic Technology                                | 236  |

|    | 14.3 — The Cofired Ceramic Tape Process                               | 237  |

|    | 14.4 — High Temperature Cofired Ceramic HTCC                          |      |

|    | 14.5 — Low Temperature Co-fired Ceramic LTCC                          |      |

|    | 14.6 — Comparing Thick Film, HTCC and LTCC                            |      |

|    | 14.7 — Advanced LTCC Processes                                        |      |

|    | 14.8 — Summary Co-fired Ceramic Process Technologies                  | 243  |

| 15 | Substrate Manufacturing Technologies: Organic Package                 | 25   |

|    | and Interconnect Substrate                                            |      |

|    |                                                                       |      |

| 1  | 15 — THE LEVEL 2.0 PRINTED WIRING BOARD                               |      |

|    | 15.1 — Overview of Conventional MLB Processing                        |      |

|    | 15.2 — The PBGA and the MCM-L                                         | 248  |

### Table of Contents

| 15.3 — Impact of the IC on Packaging and Interconnect Technology |     |

|------------------------------------------------------------------|-----|

| 15.4 — Vias and HDI                                              | 251 |

| 15.5 — IBM's SLC and HDI PWB Build Up Technology (BUT)           | 253 |

| 15.6 — Current Status Microvia HDI PWBs                          | 256 |

| 15.7 — Enhancing HDI PWBs—Embedded Passives                      | 257 |

| 15.8 — Technology Status                                         | 259 |

| Acronymns and Definitions                                        | 261 |

| Microelectronics Glossary                                        | 265 |

| Index                                                            | 289 |

# **List of Figures**

| Figure 1-1. Moore's Law                                                  | 2  |

|--------------------------------------------------------------------------|----|

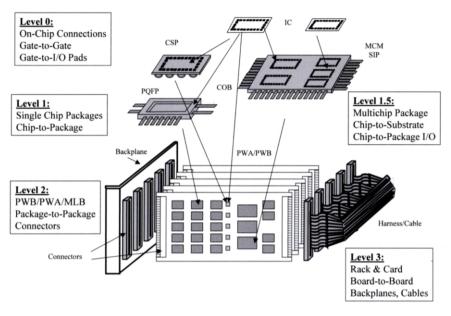

| Figure 1-2. The Electronic Manufacturing Process                         | 4  |

| Figure 1-3(a). Single Chip Packaging                                     | 5  |

| Figure 1-3(b). Multichip Packaging                                       | 5  |

| Figure 1-3(c). Chip On Board                                             | 6  |

| Figure 1-4(a). Chip & Wire                                               | 6  |

| Figure 1-4(b). TAB                                                       | 6  |

| Figure 1-4(c). Flip Chip                                                 | 7  |

| Figure 1-5. Printed Circuit Board (PCB) or Printed Wiring Board Assembly |    |

| (PWBA)                                                                   | 7  |

| Figure 1-6. IC circa 1970, Single Level Al Metallization ≈20 Micrometers |    |

| Minimum Line Width                                                       | 8  |

| Figure 1-7(a). IC circa 2000, Multilevel Metallization                   | 9  |

| Figure 1-7(b). SEM Photomicrograph Multilevel Copper Interconnect,       |    |

| Minimum Line Width ≈2 micrometers                                        | 9  |

| Figure 1-8(a). Peripheral and Area Array I/O formats                     |    |

| Figure 1-8(b). I/O Capabilities: Peripheral Format vs. Area Array        |    |

| Figure 1-9. Area Array Packages—BGAs                                     | 14 |

| 8 , 0                                                                    |    |

| Figure 2-1. A 300 mm (12") and 200 mm (8") Diameter Silicon Wafer        | 16 |

| Figure 2-2. Schematic Cross-Section of a Si Integrated Circuit           |    |

| Figure 2-3. A Class 1 Cluster Cell within a Class 10 Cleanroom           |    |

| Figure 2-4. Robotic Wafer Handling                                       |    |

| Figure 2-5. Si Wafer Fab, The Front End Processes                        |    |

| Figure 2-6. The Basic Pattern Transfer Process                           |    |

| Figure 2-7(a). An Array Photomask                                        |    |

| Figure 2-7(b). A Reticle                                                 |    |

| Figure 2-8. Deposition of Liquid Photoresist by Spinning                 | 24 |

| Figure 2-9. Positive and Negative Acting Photoresist                     | 25 |

| Figure 2-10. The Basic Exposure System                                   | 26 |

| Figure 2-11. (a) Contact Printer; (b) Proximity Printer                  | 26 |

| Figure 2-12. Projection Printer                                          | 27 |

| Figure 2-13. The Wafer Stepper Projection System                         | 28 |

| Figure 2-14. The Step and Scan Projection System                         | 28 |

|                                                                          |    |

| Figure 3-1. Transistor and an Early IC Package (TO-5 Outline)            | 31 |

| Figure 3-2. IC Package History and Trends                                |    |

| Figure 3-3(a). Ceramic and Plastic Dual Inline Packages                  |    |

| Figure 3-3(b). PCB with Through-Hole Solder Attached DIPs                |    |

| Figure 3-4(a). Small Outline IC Packages (SOIC)                          |    |

| Figure 3-4(b). PCB with Surface Mounted Components                       | 35 |

|                                                                          |    |

| Figure 3-5. Plastic Quad Flat Pack, PQFP                                                 | 35               |

|------------------------------------------------------------------------------------------|------------------|

| Figure 3-6. Peripheral leaded Package vs. Area Array Package                             |                  |

| Figure 3-7. The Pin Grid Array Package (PGA)                                             |                  |

| Figure 3-8(a). BGA Package                                                               | 37               |

| Figure 3-8(b). BGA—Typical Bump Diameters And Pitch                                      | 37               |

| Figure 3-9. Ceramic BGA Configurations                                                   |                  |

| Figure 3-10. Ceramic BGA, Ceramic Column BGA, Pad BGA                                    |                  |

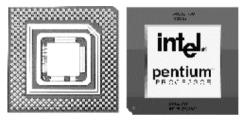

| Figure 3-11. Intel's Pentium 4 in Plastic BGA                                            |                  |

| Figure 3-12. PBGA Configurations with Rigid Laminate                                     | 39               |

| Figure 3-13. Schematic Flip Chip in Package (FCIP) PBGA                                  | 40               |

| Figure 3-14. Tape BGA Configurations                                                     |                  |

| Figure 3-15. CBGA, PBGA, TBGA                                                            |                  |

|                                                                                          |                  |

| Figure 4-1. BGA vs. CSP                                                                  | 47               |

| Figure 4-2. CSP Packages                                                                 |                  |

| Figure 4-3(a). Lead Frame Based CSP (Small Outline No-Leads, SON)                        | 49               |

| Figure 4-3(b). Laminate-Based CSP                                                        | 49               |

| Figure 4-3(c). Tape Based CSP                                                            | 50               |

| Figure 4-4. The CSP Loop                                                                 | 50               |

| Figure 4-5. Schematic of CSP on Rigid Organic Substrate                                  |                  |

| Figure 4-6(a). Embedded CSP                                                              | 51               |

| Figure 4-6(b). Metallurgical Cross-Section Embedded CSP                                  | 52               |

| Figure 4-7(a). Chip & Wire Bonded µBGA <sup>™</sup> (Face-Up)                            |                  |

| Figure 4-7(b). The µBGA <sup>™</sup> Tape Lead Bonded Face-Down                          |                  |

| Figure 4-8. µBGA™ "Interposer" Tape Format and a Singulated CSP                          |                  |

| Figure 4-9. µBGA <sup>™</sup> Lead Bonding Assembly Process                              |                  |

| Figure 4-10. µBGA™ Lead Bonding Die Attach                                               |                  |

| Figure 4-11. µBGA™ Structured Compliancy                                                 |                  |

| Figure 4-12. The UltraCSP <sup>®</sup> Process                                           |                  |

| Figure 4-13. WL-CSP                                                                      |                  |

| Figure 4-14. The ShellCase CSP                                                           |                  |

| Figure 4-15. Flip Chip International's <i>Ultra</i> CSP <sup>®</sup> with Polymer Collar | <i>5</i> /<br>58 |

|                                                                                          |                  |

| Figure 5-1. Multichip vs. Single Chip Packaging                                          | 61               |

| Figure 5-2. Hybrid Circuit with Transistors and Diodes (Circa 1960s)                     |                  |

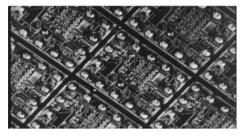

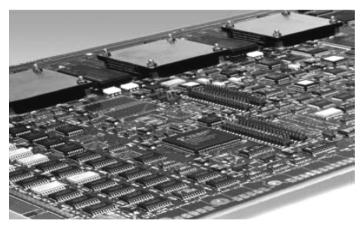

| <b>Figure 5-3.</b> Multiple ICs on Multilevel Thick Film Conductor Pattern (Circa        |                  |

| early 1980s)                                                                             | 64               |

| Figure 5-4. RF/Microwave Hybrid Circuit                                                  |                  |

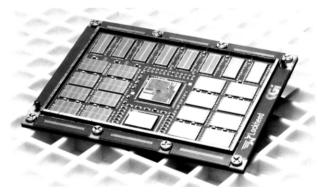

| Figure 5-5(a). MCM-D (mounted on PWB)                                                    |                  |

| Figure 5-5(b). MCM-C Cofired Ceramic Package                                             |                  |

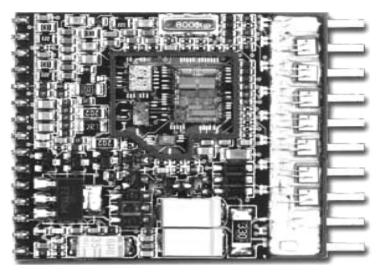

| <b>Figure 5-5(c).</b> Laminate MCM-L in Molded BGA Package. Top—Molded                   |                  |

| Package; Left—Wire Bonded ICs; Right—Bottom of Package                                   | 66               |

| Figure 5-6. Earliest 3-D Packaging: The RCA Micromodule                                  |                  |

| Figure 5-7. 3-D IC Stacking Options                                                      |                  |

| Figure 5-8. Stacked TSOPs                                                                |                  |

| Figure 5-9. (a) Schematic 3-D Memory Cube; (b) TI's 3-D Memory Cube                      |                  |

| Figure 5-10(a). Wire Bonded Stacked Die                                                  |                  |

| Ligure e re(u). Il le Dollaca Suchea Die                                                 |                  |

xiv

### List of Figures

| Figure 5-10(b). 2 Die Stack Flip Chip/Wire Bonded                                    | 70   |

|--------------------------------------------------------------------------------------|------|

| Figure 5-11. A 2 Die Stacking/Package Process Flow                                   | 70   |

| Figure 5-12. 3 Die Stack                                                             | 71   |

| Figure 5-13. SEM of a 4 Stacked Die Assembly with 2 Spacers                          | 71   |

| Figure 5-14. Various Stacked Die Configurations                                      | 72   |

| Figure 5-15. Folded Flex: Hearing Aid Application                                    | 72   |

| Figure 5-16. Folded Flex Stacked Packages                                            | 73   |

| Figure 5-17(a). Flex inner layers with Packaged and Unpackaged Components            | 73   |

| Figure 5-17(b). Finished Cube Showing Inner Layer Interconnections                   | 73   |

| Figure 5-18. (a) Single Chip Neo-Stack <sup>™</sup> inner layer; (b) Multichip Inner |      |

| Layer                                                                                | 74   |

| Figure 5-18(c). 19-Layer Smart Flash Stack including Two Neo-Stack™                  |      |

| Layers                                                                               | 74   |

| Figure 5-19(a). Vertical Integration Silicon Through-Via Die-to-Die Stacking         |      |

| Process                                                                              | 76   |

| Figure 5-19(b). Cu filled Silicon Through Vias                                       |      |

| Figure 5-20. Schematic Cross-Section of Vertically Interconnected Stacked            |      |

| Die                                                                                  | 77   |

| Figure 5-21. MCM vs. SiP vs. SoP                                                     |      |

| Figure 5-22. Cost/Benefits SiP/SoP vs. SoC                                           |      |

| 0                                                                                    |      |

| Figure 6-1. (a) IC Wafer on Film Frame; (b) Wafer Sawing                             | 82   |

| Figure 6-2. Waffle Pack, Gel-Pak®, Tape, Film Frame                                  |      |

| Figure 6-3. IC Plastic Encapsulated Package Process                                  |      |

| Figure 6-4. MCP Assembly/Test Process Flow                                           |      |

| Figure 6-5. Multichip Assembly/Electrical Yield vs. Electrical Yield of Die          |      |

| Figure 6-6. The DiePak Die Carrier                                                   |      |

| Figure 6-7. Die Flow for Package Device and KGD Die in Temporary Carrier             |      |

| Figure 6-8. KGD Testing—Options 2, 3, 4                                              |      |

| Figure 6-9. Cost/Reliability Tradeoffs                                               |      |

| Figure 6-10. Wafer Level Burn-in and Test                                            |      |

| 0                                                                                    |      |

| Figure 7-1. (left) Chip on Board Assembly; (right) MCM-L                             | 93   |

| Figure 7-2. SMT/COB Assembly                                                         |      |

| Figure 7-3(a). COB Assembly: Die Attach, Wire Bonding, Encapsulation                 |      |

| (Glob Top)                                                                           | 95   |

| Figure 7-3. (b) Wedge Bonding on PWB; (c) Ball Bonding on PWB                        |      |

| Figure 7-4. Assemblies Before and After Glob Top Encapsulation                       |      |

| Figure 7-5. SMT/COB Process Flow                                                     |      |

| Figure 7-6. Flip Chip/SMT Assembly Process                                           |      |

| Figure 7-7. SMT/Flip Chip On Board, FCOB                                             |      |

| Figure 7-8. Comparing QFP, TAB, COB, Flip Chip Footprint on PWB                      |      |

|                                                                                      |      |

| Figure 8-1. Classic Wedge Wire Bond                                                  | .103 |

| Figure 8-2. Classic Wire Ball Bond                                                   |      |

|                                                                                      |      |

| Figure 8-3. IC Assembly Process for PEMs                                             | .106 |

| Figure 8-5. Metallurgical Cross Sections of Au and Cu Ball Bonds on Al with |     |

|-----------------------------------------------------------------------------|-----|

| Data on Growth Rates at Elevated Temperatures                               |     |

| Figure 8-6. Bonding Tools—Capillary and Wedge Bonding Tools                 | 110 |

| Figure 8-7. SEM Au Ball Bond and Al Wedge Bond                              |     |

| Figure 8-8. The Ball Bonding Process                                        |     |

| Figure 8-9. The Wedge Bonding Process                                       |     |

| Figure 8-10. SEM—Thick Film and EDAX Analysis                               |     |

| Figure 8-11. Wire Bonding on Screen Printed Thick Film                      |     |

| Figure 8-12. Schematic Ball Shear (left) and Wire Pull Testing (right)      |     |

| Figure 8-13. Wire Bonding Failure Modes/Sites                               |     |

| Figure 8-14(a). Two and Three Staggered Row I/O Pad Configurations          |     |

| Figure 8-14(b). 3 Staggered Rows of Bond Pads                               |     |

| Figure 8-15. Capillary Re-Design for Fine Pitch Applications                | 122 |

| Figure 8-16. Fine Pitch Ball Bonding                                        |     |

| Figure 8-17. PBGA Showing Fan Out of Package Pads and Long Loop Wire        |     |

| Bonds                                                                       | 123 |

| Figure 8-18. No Sweep Encapsulant                                           |     |

| Figure 8-19. High Density Fine Pitch Wire Bonding with Insulated Wires      |     |

| Figure 8-20. Wire Bonding Responding to Changing Packaging Technologies.    |     |

| Figure 8-21. Bond Pad "Cupping" on "Soft" Substrate                         | 127 |

| 5 11 6                                                                      |     |

| Figure 9-1. Schematic of a Single Frame TAB Assembly                        | 130 |

| Figure 9-2. Microprocessor IC TAB Tape—35mm Tape                            |     |

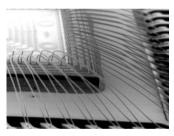

| Figure 9-3. Close-up of TAB Tape (70 mm) for Very High I/O Count IC         |     |

| Figure 9-4. Types of TAB Tapes                                              |     |

| Figure 9-5. Tape Layout with Annular Ring                                   |     |

| Figure 9-6. Excised TAB Assembly in Carrier for Testing                     |     |

| Figure 9-7(a). Schematic Bumped Die TAB                                     |     |

| Figure 9-7(b). Bumped Tape TAB                                              |     |

| Figure 9-7(c). TAB Lead on Al Pad                                           |     |

| Figure 9-8. TAB Inner Lead Bonding Process                                  |     |

| Figure 9-9. TAB Package/Substrate Attachment Options                        |     |

| Figure 9-10. Face Up and Flip TAB Bonding                                   |     |

| Figure 9-11. TAB Failure Sites                                              | 138 |

| Figure 9-12. Microprocessor Module (~5"x5") with all TAB Device Assembly    | 140 |

| 5 1 ,                                                                       |     |

| Figure 10-1. (a) IBM's Flip Chip Transistor; (b) Multichip Transistor       |     |

| Assembly                                                                    | 144 |

| Figure 10-2. IC with Bumps Directly on Bond Pads                            | 144 |

| Figure 10-3. IC I/O Pad Formats: (L to R) Dual Row Peripheral, Peripheral + |     |

| Partial, Area Array                                                         | 145 |

| Figure 10-4(a). Direct Bump on Pad                                          |     |

| Figure 10-4(b). Schematic Redistribution Layer (RDL)                        |     |

| Figure 10-4(c). Schematic of Relocated Pad and Bump                         |     |

| Figure 10-4(d). SDRAM Flip Chip with Redistributed Bond Pads                |     |

| Figure 10-5(a). Al Pad as Received                                          |     |

|                                                                             |     |

| Figure 10-5(b). Al Pad after Electroless Ni/Immersion Au Plating (5 microns                                                                                                                                                                                                                                                                                                                  |                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| thick)                                                                                                                                                                                                                                                                                                                                                                                       | 150                                                                                                                             |

| Figure 10-6. Ball Placement by Vacuum Process                                                                                                                                                                                                                                                                                                                                                | 151                                                                                                                             |

| Figure 10-7(a). The Evaporation Bumping Process (C-4)                                                                                                                                                                                                                                                                                                                                        | 152                                                                                                                             |

| Figure 10-7(b). Schematic of C-4 Evaporated Bump Before and After Reflow                                                                                                                                                                                                                                                                                                                     | 153                                                                                                                             |

| Figure 10-7(c). Solder Dammed Substrate Pad (C-4)                                                                                                                                                                                                                                                                                                                                            | 153                                                                                                                             |

| Figure 10-8. The Electroplated Solder Bumping Process                                                                                                                                                                                                                                                                                                                                        | 154                                                                                                                             |

| Figure 10-9. Schematic Cross-section of Bump Site Pre-Plating and AS-Plated                                                                                                                                                                                                                                                                                                                  |                                                                                                                                 |

| Bump                                                                                                                                                                                                                                                                                                                                                                                         | 155                                                                                                                             |

| Figure 10-10. SEM Electroplated Cu Bumps                                                                                                                                                                                                                                                                                                                                                     | 155                                                                                                                             |

| Figure 10-11. Electroplated Au Bumps                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                 |

| Figure 10-12(a). Wafer Bumping Process Using Stencil Printing                                                                                                                                                                                                                                                                                                                                | 157                                                                                                                             |

| Figure 10-12(b). Bumping by Stencil Printing                                                                                                                                                                                                                                                                                                                                                 | 157                                                                                                                             |

| Figure 10-13(a). C4NP Mold with Cavities Corresponding to Bump Locations                                                                                                                                                                                                                                                                                                                     | 158                                                                                                                             |

| Figure 10-13(b). Molten Solder Filling of Mold Cavities                                                                                                                                                                                                                                                                                                                                      | 158                                                                                                                             |

| Figure 10-13(c). Molten Solder Bump Transfer to Wafer                                                                                                                                                                                                                                                                                                                                        | 158                                                                                                                             |

| Figure 10-14. Continuous Mode Solder Jet Technology                                                                                                                                                                                                                                                                                                                                          | 159                                                                                                                             |

| Figure 10-15. (a) Schematic Cross-section of NiAu Bump; (b) 20µm                                                                                                                                                                                                                                                                                                                             |                                                                                                                                 |

| Ni-Au Bump                                                                                                                                                                                                                                                                                                                                                                                   | 160                                                                                                                             |

| Figure 10-16. Stencil Printed Conductive Epoxy Bump (75µm)                                                                                                                                                                                                                                                                                                                                   | 162                                                                                                                             |

| Figure 10-17. Elastomeric Bumps                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                 |

| Figure 10-18. Au Stud Bumps as Bonded and After Coining                                                                                                                                                                                                                                                                                                                                      | 164                                                                                                                             |

| Figure 10-19. Coined Stud Bumps As Bonded                                                                                                                                                                                                                                                                                                                                                    | 164                                                                                                                             |

| Figure 10-20. Stacked and Area Array Stud Bumps                                                                                                                                                                                                                                                                                                                                              | 165                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                 |

| Figure 11-1. (right) Manual Flip Chip Aligner Bonder; (left) Schematic of                                                                                                                                                                                                                                                                                                                    |                                                                                                                                 |

| Bi-directional Viewing of Die and Package/Substrate Footprint                                                                                                                                                                                                                                                                                                                                |                                                                                                                                 |

| Bi-directional Viewing of Die and Package/Substrate Footprint<br>Figure 11-2. Solder Reflow Options                                                                                                                                                                                                                                                                                          | 171                                                                                                                             |

| Bi-directional Viewing of Die and Package/Substrate Footprint<br>Figure 11-2. Solder Reflow Options<br>Figure 11-3. Flip Chip Solder Reflow Process                                                                                                                                                                                                                                          | 171<br>172                                                                                                                      |

| Bi-directional Viewing of Die and Package/Substrate Footprint<br>Figure 11-2. Solder Reflow Options<br>Figure 11-3. Flip Chip Solder Reflow Process<br>Figure 11-4. Solder Reflow and Self-Alignment                                                                                                                                                                                         | 171<br>172<br>172                                                                                                               |

| Bi-directional Viewing of Die and Package/Substrate Footprint<br>Figure 11-2. Solder Reflow Options<br>Figure 11-3. Flip Chip Solder Reflow Process<br>Figure 11-4. Solder Reflow and Self-Alignment<br>Figure 11-5. SMT/Flip Chip Assembly                                                                                                                                                  | 171<br>172<br>172<br>173                                                                                                        |

| Bi-directional Viewing of Die and Package/Substrate Footprint<br>Figure 11-2. Solder Reflow Options<br>Figure 11-3. Flip Chip Solder Reflow Process<br>Figure 11-4. Solder Reflow and Self-Alignment<br>Figure 11-5. SMT/Flip Chip Assembly<br>Figure 11-6(a). Schematic of a FCOB Solder Joint Fatigue Failure                                                                              | 171<br>172<br>172<br>173                                                                                                        |

| Bi-directional Viewing of Die and Package/Substrate Footprint<br>Figure 11-2. Solder Reflow Options<br>Figure 11-3. Flip Chip Solder Reflow Process<br>Figure 11-4. Solder Reflow and Self-Alignment<br>Figure 11-5. SMT/Flip Chip Assembly<br>Figure 11-6(a). Schematic of a FCOB Solder Joint Fatigue Failure<br>Figure 11-6(b). Metallurgical Cross-Section of Solder Fatigue Cracking in | 171<br>172<br>172<br>173<br>174                                                                                                 |

| <ul> <li>Bi-directional Viewing of Die and Package/Substrate Footprint</li> <li>Figure 11-2. Solder Reflow Options</li> <li>Figure 11-3. Flip Chip Solder Reflow Process</li> <li>Figure 11-4. Solder Reflow and Self-Alignment</li></ul>                                                                                                                                                    | 171<br>172<br>172<br>173<br>174                                                                                                 |

| <ul> <li>Bi-directional Viewing of Die and Package/Substrate Footprint</li> <li>Figure 11-2. Solder Reflow Options</li> <li>Figure 11-3. Flip Chip Solder Reflow Process</li> <li>Figure 11-4. Solder Reflow and Self-Alignment</li> <li>Figure 11-5. SMT/Flip Chip Assembly</li></ul>                                                                                                       | 171<br>172<br>172<br>173<br>174<br>175<br>175                                                                                   |

| <ul> <li>Bi-directional Viewing of Die and Package/Substrate Footprint</li> <li>Figure 11-2. Solder Reflow Options</li> <li>Figure 11-3. Flip Chip Solder Reflow Process</li> <li>Figure 11-4. Solder Reflow and Self-Alignment</li> <li>Figure 11-5. SMT/Flip Chip Assembly</li> <li>Figure 11-6(a). Schematic of a FCOB Solder Joint Fatigue Failure</li></ul>                             | <ul> <li>171</li> <li>172</li> <li>172</li> <li>173</li> <li>174</li> <li>175</li> <li>175</li> <li>176</li> </ul>              |

| <ul> <li>Bi-directional Viewing of Die and Package/Substrate Footprint</li> <li>Figure 11-2. Solder Reflow Options</li> <li>Figure 11-3. Flip Chip Solder Reflow Process</li></ul>                                                                                                                                                                                                           | <ol> <li>171</li> <li>172</li> <li>172</li> <li>173</li> <li>174</li> <li>175</li> <li>175</li> <li>176</li> <li>177</li> </ol> |

| <ul> <li>Bi-directional Viewing of Die and Package/Substrate Footprint</li> <li>Figure 11-2. Solder Reflow Options</li> <li>Figure 11-3. Flip Chip Solder Reflow Process</li></ul>                                                                                                                                                                                                           | <ol> <li>171</li> <li>172</li> <li>172</li> <li>173</li> <li>174</li> <li>175</li> <li>175</li> <li>176</li> <li>177</li> </ol> |

| <ul> <li>Bi-directional Viewing of Die and Package/Substrate Footprint</li> <li>Figure 11-2. Solder Reflow Options</li> <li>Figure 11-3. Flip Chip Solder Reflow Process</li> <li>Figure 11-4. Solder Reflow and Self-Alignment</li> <li>Figure 11-5. SMT/Flip Chip Assembly</li></ul>                                                                                                       | 171<br>172<br>172<br>173<br>174<br>175<br>175<br>176<br>177<br>178                                                              |

| <ul> <li>Bi-directional Viewing of Die and Package/Substrate Footprint</li> <li>Figure 11-2. Solder Reflow Options</li> <li>Figure 11-3. Flip Chip Solder Reflow Process</li> <li>Figure 11-4. Solder Reflow and Self-Alignment</li></ul>                                                                                                                                                    | 171<br>172<br>172<br>173<br>174<br>175<br>175<br>176<br>177<br>178<br>178                                                       |

| <ul> <li>Bi-directional Viewing of Die and Package/Substrate Footprint</li> <li>Figure 11-2. Solder Reflow Options</li></ul>                                                                                                                                                                                                                                                                 | 171<br>172<br>172<br>173<br>174<br>175<br>175<br>176<br>177<br>178<br>178                                                       |

| <ul> <li>Bi-directional Viewing of Die and Package/Substrate Footprint</li> <li>Figure 11-2. Solder Reflow Options</li> <li>Figure 11-3. Flip Chip Solder Reflow Process</li></ul>                                                                                                                                                                                                           | 171<br>172<br>172<br>173<br>174<br>175<br>175<br>176<br>177<br>178<br>178<br>178                                                |

| <ul> <li>Bi-directional Viewing of Die and Package/Substrate Footprint</li> <li>Figure 11-2. Solder Reflow Options</li></ul>                                                                                                                                                                                                                                                                 | 171<br>172<br>172<br>173<br>174<br>175<br>175<br>176<br>177<br>178<br>178<br>178<br>179<br>180                                  |

| <ul> <li>Bi-directional Viewing of Die and Package/Substrate Footprint</li> <li>Figure 11-2. Solder Reflow Options</li></ul>                                                                                                                                                                                                                                                                 | 171<br>172<br>172<br>173<br>174<br>175<br>175<br>176<br>177<br>178<br>178<br>178<br>179<br>180                                  |

| <ul> <li>Bi-directional Viewing of Die and Package/Substrate Footprint</li> <li>Figure 11-2. Solder Reflow Options</li></ul>                                                                                                                                                                                                                                                                 | 171<br>172<br>172<br>173<br>174<br>175<br>175<br>175<br>176<br>177<br>178<br>178<br>179<br>180<br>185                           |

| <ul> <li>Bi-directional Viewing of Die and Package/Substrate Footprint</li> <li>Figure 11-2. Solder Reflow Options</li></ul>                                                                                                                                                                                                                                                                 | 171<br>172<br>172<br>173<br>174<br>175<br>175<br>175<br>176<br>177<br>178<br>178<br>179<br>180<br>185                           |

| Figure 11-17. Non-conductive Adhesive FC Bonding Contact Resistance vs.        |     |

|--------------------------------------------------------------------------------|-----|

| Applied Force                                                                  | 187 |

| Figure 11-18. Conductive Polymer Bumps and Attachment                          | 189 |

|                                                                                |     |

| Figure 12-1. Thin Film Cleanroom                                               |     |

| Figure 12-2. Subtractive Etch and Selective Plate Up Patterning Processes      |     |

| Figure 12-3. Thin Film Process for WL-CSP (Ultra CSP®)                         |     |

| Figure 12-4. Dry Film Lamination and Patterning                                | 198 |

| Figure 12-5. (Left) Dry Film Applied Over Previously Patterned Structure;      |     |

| (Right) Substrate Vias or Holes                                                | 198 |

| Figure 12-6. Electrodeposited Resist: Patterned for Selective Plate-up of 25um |     |

| Lines Over Previously Patterned 45um Thick 100um Wide Feature                  |     |

| Figure 12-7. Subtractive Etch Process; The "Etch Factor"                       |     |

| Figure 12-8. Planarization of a Deposited Dielectric                           |     |

| Figure 12-9. Photodefineable vs. Photosensitive (+/-) Via Patterning           |     |

| Figure 12-10. Achievable Via Diameters Using Laser and Photo-Patterning        | 207 |

| Figure 12-11. Metallurgical Cross-Section Thin Film Multilayer Interconnect    |     |

| on Ceramic Substrate                                                           | 208 |

| Figure 12-12. Thin Film Interconnects on Co-fired Ceramic Substrate            | 209 |

| Figure 12-13. Thin Film Multilayer Interconnect on PWB (MCM-L/D)               | 209 |

| Figure 12-14. Si Substrate Supporting Multilevel Thin Film Interconnect for    |     |

| MCM                                                                            | 210 |

| Figure 12-15. Schematic Cross-Section of a Si Substrate with Embedded          |     |

| Active and Passive Devices                                                     | 211 |

| Figure 12-16. DRAM Chips Flip Chip Assembled on Electrically Tested            |     |

| ASICs                                                                          | 211 |

| Figure 12-17. GE HDI "Chips First" MCM                                         |     |

| Figure 12-18. The "Chips First" (GE HDI) MCM Process Flow                      |     |

| Figure 12-19. GE HDI MCM and SMT Printed Circuit Board Assembly                |     |

| Figure 12-20. The Low Cost GE HDI or Embedded Chip Build Up (ECBU)             |     |

| Process                                                                        | 214 |

| Figure 12-21(a). An ECBU MCM with Embedded Active and Passives                 |     |

| Figure 12-21(b). An ECBU MCM with Embedded Actives and Passives and            |     |

| Package Devices and Discrete Passives Mounted on Top Layer                     | 215 |

| Figure 12-22. The Intel BBUL Process for Microprocessors                       |     |

| Figure 12-23. Intel's Current Microprocessor Package and the BBUL              |     |

| Figure 12-24. Intel's Multichip BBUL                                           |     |

| Figure 12-25. Substrate Size/Yield and Defect Density                          |     |

| Figure 12-25. Substrate Size Tield and Defect Defisity                         |     |

| Figure 13-1. The Multilayer Thick Film Process Sequence                        | 222 |

| Figure 13-2(a). Photo-Patterned Emulsion (2 mils 1/s) on 360 SS Mesh           | 224 |

| Figure 13-2(b). Fully Patterned Screen                                         |     |

| Figure 13-3. Screen Printing Process                                           |     |

| Figure 13-4. Manual Screen Printer                                             |     |

| Figure 13-5. Thick Film Printing Variables Requiring Monitoring                |     |

| Figure 13-6. Automatic Thick Film Screen Printer                               |     |

| Figure 13-7. Screen Printed Thick Film Au Conductor trace                      |     |

| Figure 13-8(a). Thick Film Multilayer Interconnect Board (MIB)                               | 228  |

|----------------------------------------------------------------------------------------------|------|

| Figure 13-8(b). Cofired Ceramic MIBs Populated with Ceramic Chip Carrier                     |      |

| Packages                                                                                     | .229 |

| Figure 13-9. Diffusion Patterning <sup>TM</sup> Process                                      | .230 |

| Figure 13-10. Dupont Fodel® Photosensitive Thick Film Paste Processing                       |      |

| Figure 13-11(a). Photo-Patterned 50 um Via in Thick Film Dielectric                          | .231 |

| Figure 13-11(b). Photo-Patterned Thick Film Au Conductor Traces;                             |      |

| Left: 28 um lines, 22 um spaces; Right: 50 um lines, 4.5 um thick                            | .232 |

|                                                                                              |      |

| Figure 14-1. Patent on Cofired Ceramic Manufacture Issued to Harold                          | 222  |

| W. Stetson, RCA                                                                              |      |

| Figure 14-2(a). IBM Thermal Conduction Module (TCM)                                          |      |

| Figure 14-2(b). Cross-Section of TCM Ceramic Substrate Interconnect                          |      |

| Figure 14-3(a). Next Generation TCM                                                          | .235 |

| Figure 14-3(b). A Cofired Ceramic Package with Thin Film Signal Layers and                   | 226  |

| Top Layer Metallization                                                                      |      |

| Figure 14-4. Unfired ("Green") Ceramic Tape                                                  |      |

| Figure 14-5. Cofired Ceramic Optional Instruction Features (LTCC)                            |      |

| Figure 14-6. The Cofired Ceramic Tape Process                                                |      |

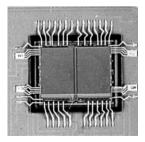

| Figure 14-7(a). HTCC Hermetic Single and Multichip Packages                                  | .239 |

| Figure 14-7(b). HTCC Multilayer Interconnect Board with Select Areas for                     | 220  |

| Hermetic Sealing                                                                             |      |

| Figure 14-8. LTCC Multichip Packages                                                         |      |

| Figure 14-9. LTCC-M, A Constrained Cofired Ceramic Tape Process                              | .242 |

| <b>Figure 14-10.</b> Large Area Panel (7"x 11") Using Heralock <sup>™</sup> Self-Constrained | 242  |

| LTCC Tape                                                                                    | .243 |

| Figure 15-1(a). Multilayer PWB with Plated-Through Holes                                     | 246  |

| Figure 15 1(u). Plated Through-Hole Via                                                      |      |

| Figure 15-1(b): Flater Inforgin Flore Via                                                    |      |

| Figure 15-3(a). Schematic Plastic BGA                                                        |      |

| Figure 15-3(b). PBGAs in Strip Format and After Epoxy Molding/Singulation                    |      |

| Figure 15-4(a). Unpopulated MCM-L Substrate                                                  |      |

| Figure 15-4(b). MCM-L—Multichip Module with Laminate Substrate                               |      |

| Figure 15-5. Through-Hole, Blind, and Buried Vias                                            |      |

| Figure 15-6. Effect of Via Type on Board Size                                                |      |

| Figure 15-7. Methods of Via Generation                                                       |      |

| Figure 15-8(a). Schematic IBM's Surface Laminar Circuit-SLC BGA                              |      |

| Figure 15-8(b). Cross-section SLC Flip Chip Package                                          |      |

| Figure 15-9. Single Chip SLC/BUT PBGA                                                        |      |

| Figure 15-10. Key Feature Dimensions for the HDI PWB                                         |      |

| Figure 15-11. The HDBU and Super HDBU                                                        |      |

| Figure 15-12. Cross-section Super-HDBU 2–3–2 PWB                                             |      |

| Figure 15-13. Multilayer and Microvia PWB Projections                                        |      |

| Figure 15-14. Cell Phone Key Features and Component Count                                    |      |

| Figure 15-15. Embedded Discrete Capacitor                                                    |      |

| Figure 15-16. Discrete vs. Embedded Planar Decoupling Capacitor                              |      |

# List of Tables

| Table 1-1. Overall IC Characteristics (ITRS Technology Roadmap                                                                                         | 1 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| (ITRS 2005))                                                                                                                                           |   |

| Table 1-2. Single Chip Fill Count (TTKS 2003)                                                                                                          | 1 |

| Table 2-1. Cleanroom Classifications [US FED STD 209E Cleanroom                                                                                        |   |

| Standards]1                                                                                                                                            | 8 |

| Table 2-2. Comparison of Positive and Negative Resists         2                                                                                       | 5 |

|                                                                                                                                                        |   |

| Table 5-1. Comparing DIP, SMT, MCP at System Level (Courtesy Hughes         Aircraft)                                                                  | 2 |

| <b>Table 5-2.</b> Advantages of System on Package vs. System On Chip7                                                                                  |   |

| Table 3-2. Advantages of System on Lackage vs. System on Chip                                                                                          | 0 |

| Table 7-1. Encapsulants for COB    9                                                                                                                   | 7 |

| Table 7-2. COB vs. FCOB/WLP                                                                                                                            |   |

|                                                                                                                                                        |   |

| Table 8-1. Eutectic vs. Adhesive Bonding10                                                                                                             |   |

| Table 8-2. Material Properties of Al, Cu, and Au Wire10                                                                                                |   |

| Table 8-3(a).         Advantages/Disadvantages of Thermocompression Bonding         10                                                                 |   |

| Table 8-3(b).       Advantages/Disadvantages of Ultrasonic Bonding                                                                                     |   |

| Table 8-3(c).       Advantages/Disadvantages of Thermosonic Bonding                                                                                    |   |

| Table 8-4. Sources of Contamination that Lead to Poor Quality Bonds                                                                                    |   |

| Table 8-5. Metallurgical Compatibility of Wire bonding Materials.       11         Table 9. (c)       Au Wire Destructive Bull Tast Criteria.       11 |   |

| Table 8-6(a). Au Wire Destructive Pull Test Criteria       11         Table 8-6(b). Al Wire Destructive Pull Test Criteria       11                    |   |

| Table 8-6(b). At whe Destructive Pull Test Chiefia                                                                                                     | 9 |

| Table 9-1. Key Elements of a TAB Assembly                                                                                                              | 0 |

| Table 9-2. Comparing Tape Options                                                                                                                      |   |

| Table 9-3. Comparison TAB Inner Lead Bonding Techniques         13                                                                                     |   |

|                                                                                                                                                        |   |

| Table 10-1. Reflow Temperatures for Common Solder Bump Materials14                                                                                     |   |