## ADVANCED SIGNAL INTEGRITY FOR HIGH-SPEED DIGITAL DESIGNS

STEPHEN H. HALL HOWARD L. HECK

of Engineering the Future

A JOHN WILEY & SONS, INC., PUBLICATION

ADVANCED SIGNAL INTEGRITY FOR HIGH-SPEED DIGITAL DESIGNS

## ADVANCED SIGNAL INTEGRITY FOR HIGH-SPEED DIGITAL DESIGNS

STEPHEN H. HALL HOWARD L. HECK

of Engineering the Future

A JOHN WILEY & SONS, INC., PUBLICATION

Copyright © 2009 by John Wiley & Sons, Inc. All rights reserved.

Published by John Wiley & Sons, Inc., Hoboken, New Jersey. Published simultaneously in Canada.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning, or otherwise, except as permitted under Section 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, Inc., 222 Rosewood Drive, Danvers, MA 01923, (978) 750-8400, fax (978) 750-4470, or on the web at www.copyright.com. Requests to the Publisher for permission should be addressed to the Permissions Department, John Wiley & Sons, Inc., 111 River Street, Hoboken, NJ 07030, (201) 748-6011, fax (201) 748-6008, or online at http://www.wiley.com/go/permission.

Limit of Liability/Disclaimer of Warranty: While the publisher and author have used their best efforts in preparing this book, they make no representations or warranties with respect to the accuracy or completeness of the contents of this book and specifically disclaim any implied warranties of merchantability or fitness for a particular purpose. No warranty may be created or extended by sales representatives or written sales materials. The advice and strategies contained herein may not be suitable for your situation. You should consult with a professional where appropriate. Neither the publisher nor author shall be liable for any loss of profit or any other commercial damages, including but not limited to special, incidental, consequential, or other damages.

For general information on our other products and services or for technical support, please contact our Customer Care Department within the United States at (800) 762-2974, outside the United States at (317) 572-3993 or fax (317) 572-4002.

Wiley also publishes its books in a variety of electronic formats. Some content that appears in print may not be available in electronic formats. For more information about Wiley products, visit our web site at www.wiley.com.

#### Library of Congress Cataloging-in-Publication Data:

Hall, Stephen H.

Advanced signal integrity for high-speed digital designs / Stephen H. Hall, Howard L. Heck.

p. cm.

Includes bibliographical references and index.

ISBN 978-0-470-19235-1 (cloth)

1. Digital electronics. 2. Logic designs. I. Heck, Howard L. II. Title.

TK7868.D5H298 2009

621'.381-dc22

2008027977

Printed in the United States of America

10 9 8 7 6 5 4 3 2 1

## **CONTENTS**

Preface

| Preface                                               |   |

|-------------------------------------------------------|---|

| 1. Introduction: The Importance of Signal Integrity   | 1 |

| 1.1 Computing Power: Past and Future, 1               |   |

| 1.2 The Problem, 4                                    |   |

| 1.3 The Basics, 5                                     |   |

| 1.4 A New Realm of Bus Design, 7                      |   |

| 1.5 Scope of the Book, 7                              |   |

| 1.6 Summary, 8                                        |   |

| References, 8                                         |   |

| 2. Electromagnetic Fundamentals for Signal Integrity  | 9 |

| 2.1 Maxwell's Equations, 10                           |   |

| 2.2 Common Vector Operators, 13                       |   |

| 2.2.1 Vector, 13                                      |   |

| 2.2.2 Dot Product, 13                                 |   |

| 2.2.3 Cross Product, 14                               |   |

| 2.2.4 Vector and Scalar Fields, 15                    |   |

| 2.2.5 Flux, 15                                        |   |

| 2.2.6 Gradient, 18                                    |   |

| 2.2.7 Divergence, 18                                  |   |

| 2.2.8 Curl, 20                                        |   |

| 2.3 Wave Propagation, 23                              |   |

| 2.3.1 Wave Equation, 23                               |   |

| 2.3.2 Relation Between $E$ and $H$ and the Transverse |   |

| Electromagnetic Mode, 25                              |   |

| 2.3.3 Time-Harmonic Fields, 27                        |   |

|                                                       |   |

65

- 2.3.4 Propagation of Time-Harmonic Plane Waves, 28

- 2.4 Electrostatics, 32

- 2.4.1 Electrostatic Scalar Potential in Terms of an Electric Field, 36

- 2.4.2 Energy in an Electric Field, 37

- 2.4.3 Capacitance, 40

- 2.4.4 Energy Stored in a Capacitor, 41

- 2.5 Magnetostatics, 42

- 2.5.1 Magnetic Vector Potential, 46

- 2.5.2 Inductance, 48

- 2.5.3 Energy in a Magnetic Field, 51

- 2.6 Power Flow and the Poynting Vector, 53

- 2.6.1 Time-Averaged Values, 56

- 2.7 Reflections of Electromagnetic Waves, 57

- 2.7.1 Plane Wave Incident on a Perfect Conductor, 57

- 2.7.2 Plane Wave Incident on a Lossless Dielectric, 60

References, 62

Problems, 62

## 3. Ideal Transmission-Line Fundamentals

- 3.1 Transmission-Line Structures, 66

- 3.2 Wave Propagation on Loss-Free Transmission Lines, 67

- 3.2.1 Electric and Magnetic Fields on a Transmission Line, 68

- 3.2.2 Telegrapher's Equations, 73

- 3.2.3 Equivalent Circuit for the Loss-Free Case, 76

- 3.2.4 Wave Equation in Terms of *LC*, 80

- 3.3 Transmission-Line Properties, 82

- 3.3.1 Transmission-Line Phase Velocity, 82

- 3.3.2 Transmission-Line Characteristic Impedance, 82

- 3.3.3 Effective Dielectric Permittivity, 83

- 3.3.4 Simple Formulas for Calculating the Characteristic Impedance, 85

- 3.3.5 Validity of the TEM Approximation, 86

- 3.4 Transmission-Line Parameters for the Loss-Free Case, 90

- 3.4.1 Laplace and Poisson Equations, 91

- 3.4.2 Transmission-Line Parameters for a Coaxial Line, 91

- 3.4.3 Transmission-Line Parameters for a Microstrip, 94

- 3.4.4 Charge Distribution Near a Conductor Edge, 100

- 3.4.5 Charge Distribution and Transmission-Line Parameters, 104

- 3.4.6 Field Mapping, 107

- 3.5 Transmission-Line Reflections, 113

- 3.5.1 Transmission-Line Reflection and Transmission Coefficient, 113

- 3.5.2 Launching an Initial Wave, 116

- 3.5.3 Multiple Reflections, 116

- 3.5.4 Lattice Diagrams and Over- or Underdriven Transmission Lines, 118

- 3.5.5 Lattice Diagrams for Nonideal Topologies, 121

- 3.5.6 Effect of Rise and Fall Times on Reflections, 129

- 3.5.7 Reflections from Reactive Loads, 129

3.6 Time-Domain Reflectometry, 134

- 3.6.1 Measuring the Characteristic Impedance and Delay of a Transmission Line, 134

- 3.6.2 Measuring Inductance and Capacitance of Reactive Structures, 137

- 3.6.3 Understanding the TDR Profile, 140

References, 140

Problems, 141

## 4. Crosstalk

4.1 Mutual Inductance and Capacitance, 146

- 4.1.1 Mutual Inductance, 147

- 4.1.2 Mutual Capacitance, 149

- 4.1.3 Field Solvers, 152

- 4.2 Coupled Wave Equations, 153

- 4.2.1 Wave Equation Revisited, 153

- 4.2.2 Coupled Wave Equations, 155

- 4.3 Coupled Line Analysis, 157

- 4.3.1 Impedance and Velocity, 157

- 4.3.2 Coupled Noise, 165

- 4.4 Modal Analysis, 177

- 4.4.1 Modal Decomposition, 178

- 4.4.2 Modal Impedance and Velocity, 180

- 4.4.3 Reconstructing the Signal, 180

- 4.4.4 Modal Analysis, 181

- 4.4.5 Modal Analysis of Lossy Lines, 192

- 4.5 Crosstalk Minimization, 193

- 4.6 Summary, 194

- References, 195

- Problems, 195

CONTENTS

## 5. Nonideal Conductor Models

- 5.1 Signals Propagating in Unbounded Conductive

- Media, 202

- 5.1.1 Propagation Constant for Conductive Media, 202

- 5.1.2 Skin Depth, 204

- 5.2 Classic Conductor Model for Transmission Lines, 205

- 5.2.1 Dc Losses in Conductors, 206

- 5.2.2 Frequency-Dependent Resistance in Conductors, 207

- 5.2.3 Frequency-Dependent Inductance, 213

- 5.2.4 Power Loss in a Smooth Conductor, 218

- 5.3 Surface Roughness, 222

- 5.3.1 Hammerstad Model, 223

- 5.3.2 Hemispherical Model, 228

- 5.3.3 Huray Model, 237

- 5.3.4 Conclusions, 243

- 5.4 Transmission-Line Parameters for Nonideal

Conductors, 244

- 5.4.1 Equivalent Circuit, Impedance, and Propagation Constant, 244

- 5.4.2 Telegrapher's Equations for a Real Conductor and a Perfect Dielectric, 246

- References, 247

Problems, 247

## 6. Electrical Properties of Dielectrics

- 6.1 Polarization of Dielectrics, 250

- 6.1.1 Electronic Polarization, 250

- 6.1.2 Orientational (Dipole) Polarization, 253

- 6.1.3 Ionic (Molecular) Polarization, 253

- 6.1.4 Relative Permittivity, 254

- 6.2 Classification of Dielectric Materials, 256

- 6.3 Frequency-Dependent Dielectric Behavior, 256

- 6.3.1 Dc Dielectric Losses, 257

- 6.3.2 Frequency-Dependent Dielectric Model: Single Pole, 257

- 6.3.3 Anomalous Dispersion, 261

- 6.3.4 Frequency-Dependent Dielectric Model: Multipole, 262

- 6.3.5 Infinite-Pole Model, 266

- 6.4 Properties of a Physical Dielectric Model, 269

- 6.4.1 Relationship Between  $\varepsilon'$  and  $\varepsilon''$ , 269

- 6.4.2 Mathematical Limits, 271

viii

- 6.5 Fiber-Weave Effect, 274

- 6.5.1 Physical Structure of an FR4 Dielectric and Dielectric Constant Variation, 275

- 6.5.2 Mitigation, 276

- 6.5.3 Modeling the Fiber-Weave Effect, 277

- 6.6 Environmental Variation in Dielectric Behavior, 279

- 6.6.1 Environmental Effects on Transmission-Line Performance, 281

- 6.6.2 Mitigation, 283

- 6.6.3 Modeling the Effect of Relative Humidity on an FR4 Dielectric, 284

- 6.7 Transmission-Line Parameters for Lossy Dielectrics and Realistic Conductors, 285

- 6.7.1 Equivalent Circuit, Impedance, and Propagation Constant, 285

- 6.7.2 Telegrapher's Equations for Realistic Conductors and Lossy Dielectrics, 291

References, 292 Problems, 292

## 7. Differential Signaling

- 7.1 Removal of Common-Mode Noise, 299

- 7.2 Differential Crosstalk, 300

- 7.3 Virtual Reference Plane, 302

- 7.4 Propagation of Modal Voltages, 303

- 7.5 Common Terminology, 304

- 7.6 Drawbacks of Differential Signaling, 305

- 7.6.1 Mode Conversion, 305

- 7.6.2 Fiber-Weave Effect, 310

## Reference, 313

Problems, 313

## 8. Mathematical Requirements for Physical Channels

- 8.1 Frequency-Domain Effects in Time-Domain Simulations, 316

- 8.1.1 Linear and Time Invariance, 316

- 8.1.2 Time- and Frequency-Domain Equivalencies, 317

- 8.1.3 Frequency Spectrum of a Digital Pulse, 321

- 8.1.4 System Response, 324

- 8.1.5 Single-Bit (Pulse) Response, 327

- 8.2 Requirements for a Physical Channel, 331

- 8.2.1 Causality, 331

297

8.2.2 Passivity, 340 8.2.3 Stability, 343 References, 345 Problems, 345

## 9. Network Analysis for Digital Engineers

- 9.1 High-Frequency Voltage and Current Waves, 349

- 9.1.1 Input Reflection into a Terminated Network, 349

- 9.1.2 Input Impedance, 353

- 9.2 Network Theory, 354

- 9.2.1 Impedance Matrix, 355

- 9.2.2 Scattering Matrix, 358

- 9.2.3 ABCD Parameters, 382

- 9.2.4 Cascading S-Parameters, 390

- 9.2.5 Calibration and Deembedding, 395

- 9.2.6 Changing the Reference Impedance, 399

- 9.2.7 Multimode S-Parameters, 400

- 9.3 Properties of Physical S-Parameters, 406

- 9.3.1 Passivity, 406

- 9.3.2 Reality, 408

- 9.3.3 Causality, 408

- 9.3.4 Subjective Examination of S-Parameters, 410

- References, 413

Problems, 413

## 10. Topics in High-Speed Channel Modeling

- 10.1 Creating a Physical Transmission-Line Model, 418

- 10.1.1 Tabular Approach, 418

- 10.1.2 Generating a Tabular Dielectric Model, 419

- 10.1.3 Generating a Tabular Conductor Model, 420

- 10.2 NonIdeal Return Paths, 422

- 10.2.1 Path of Least Impedance, 422

- 10.2.2 Transmission Line Routed Over a Gap in the Reference Plane, 423

- 10.2.3 Summary, 434

- 10.3 Vias, 434

- 10.3.1 Via Resonance, 434

- 10.3.2 Plane Radiation Losses, 437

- 10.3.3 Parallel-Plate Waveguide, 439

- References, 441

- Problems, 442

#### 347

## 11. I/O Circuits and Models

- 11.1 I/O Design Considerations, 444

- 11.2 Push-Pull Transmitters, 446

- 11.2.1 Operation, 446

- 11.2.2 Linear Models, 448

- 11.2.3 Nonlinear Models, 453

- 11.2.4 Advanced Design Considerations, 455

- 11.3 CMOS receivers, 459

- 11.3.1 Operation, 459

- 11.3.2 Modeling, 460

- 11.3.3 Advanced Design Considerations, 460

- 11.4 ESD Protection Circuits, 460

- 11.4.1 Operation, 461

- 11.4.2 Modeling, 461

- 11.4.3 Advanced Design Considerations, 463

- 11.5 On-Chip Termination, 463

- 11.5.1 Operation, 463

- 11.5.2 Modeling, 463

- 11.5.3 Advanced Design Considerations, 464

- 11.6 Bergeron Diagrams, 465

- 11.6.1 Theory and Method, 470

- 11.6.2 Limitations, 474

- 11.7 Open-Drain Transmitters, 474

- 11.7.1 Operation, 474

- 11.7.2 Modeling, 476

- 11.7.3 Advanced Design Considerations, 476

- 11.8 Differential Current-Mode Transmitters, 479

- 11.8.1 Operation, 479

- 11.8.2 Modeling, 480

- 11.8.3 Advanced Design Considerations, 480

- 11.9 Low-Swing and Differential Receivers, 481

- 11.9.1 Operation, 481

- 11.9.2 Modeling, 482

- 11.9.3 Advanced Design Considerations, 483

- 11.10 IBIS Models, 483

- 11.10.1 Model Structure and Development Process, 483

- 11.10.2 Generating Model Data, 485

- 11.10.3 Differential I/O Models, 488

- 11.10.4 Example of an IBIS File, 490

- 11.11 Summary, 492

- References, 492

Problems, 494

## 12. Equalization

12.1 Analysis and Design Background, 500

- 12.1.1 Maximum Data Transfer Capacity, 500

- 12.1.2 Linear Time-Invariant Systems, 502

- 12.1.3 Ideal Versus Practical Interconnects, 506

- 12.1.4 Equalization Overview, 511

- 12.2 Continuous-Time Linear Equalizers, 513

- 12.2.1 Passive CTLEs, 514

- 12.2.2 Active CTLEs, 521

- 12.3 Discrete Linear Equalizers, 522

- 12.3.1 Transmitter Equalization, 525

- 12.3.2 Coefficient Selection, 530

- 12.3.3 Receiver Equalization, 535

- 12.3.4 Nonidealities in DLEs, 536

- 12.3.5 Adaptive Equalization, 536

12.4 Decision Feedback Equalization, 540

- 12.5 Summary, 542

- References, 545

- Problems, 546

## 13. Modeling and Budgeting of Timing Jitter and Noise

- 13.1 Eye Diagram, 550

- 13.2 Bit Error Rate, 552

- 13.2.1 Worst-Case Analysis, 552

- 13.2.2 Bit Error Rate Analysis, 555

- 13.3 Jitter Sources and Budgets, 560

- 13.3.1 Jitter Types and Sources, 561

- 13.3.2 System Jitter Budgets, 568

- 13.4 Noise Sources and Budgets, 572

- 13.4.1 Noise Sources, 572

- 13.4.2 Noise Budgets, 579

## 13.5 Peak Distortion Analysis Methods, 583

- 13.5.1 Superposition and the Pulse Response, 583

- 13.5.2 Worst-Case Bit Patterns and Data Eyes, 585

- 13.5.3 Peak Distortion Analysis Including Crosstalk, 594

- 13.5.4 Limitations, 598

- 13.6 Summary, 599

- References, 599

- Problems, 600

499

| 14. System Analysis Using Response Surface Modeling                                                            | 605 |

|----------------------------------------------------------------------------------------------------------------|-----|

| 14.1 Model Design Considerations, 606                                                                          |     |

| 14.2 Case Study: 10-Gb/s Differential PCB Interface, 607                                                       |     |

| 14.3 RSM Construction by Least Squares Fitting, 607                                                            |     |

| 14.4 Measures of Fit, 615                                                                                      |     |

| 14.4.1 Residuals, 615                                                                                          |     |

| 14.4.2 Fit Coefficients, 616                                                                                   |     |

| 14.5 Significance Testing, 618                                                                                 |     |

| 14.5.1 Model Significance: The F-Test, 618                                                                     |     |

| 14.5.2 Parameter Significance: Individual t-Tests, 619                                                         |     |

| 14.6 Confidence Intervals, 621                                                                                 |     |

| 14.7 Sensitivity Analysis and Design Optimization, 623                                                         |     |

| 14.8 Defect Rate Prediction Using Monte Carlo                                                                  |     |

| Simulation, 628                                                                                                |     |

| 14.9 Additional RSM Considerations, 633                                                                        |     |

| 14.10 Summary, 633                                                                                             |     |

| References, 634                                                                                                |     |

| Problems, 635                                                                                                  |     |

| Appendix A: Useful Formulas, Identities, Units, and Constants                                                  | 637 |

| Appendix B: Four-Port Conversions Between <i>T</i> - and<br>S-Parameters                                       | 641 |

| Appendix C: Critical Values of the F-Statistic                                                                 | 645 |

| Appendix D: Critical Values of the T-Statistic                                                                 | 647 |

| Appendix E: Causal Relationship Between Skin Effect Resistance<br>and Internal Inductance for Rough Conductors | 649 |

| Appendix F: Spice Level 3 Model for 0.25 $\mu$ m MOSIS Process                                                 | 653 |

Index

## PREFACE

Technology has progressed to a point where digital design has entered a new realm that requires design techniques and concepts that baffle even some of the most seasoned digital system designers. The fact is that state-of-the-art digital systems such as personal computers cannot be designed without a thorough understanding of advanced signal integrity. As computer technology evolves, high-speed interconnect phenomena that designers historically have ignored begin to dominate performance, and unforeseen problems arise that dramatically increase the complexity of design. Consequently, every new generation of computer design requires an understanding of new signal integrity issues that were previously not critical and new design techniques that were previously not necessary. In modern and future systems, an incomplete understanding of high-speed interconnect phenomena will literally result in the progress of digital computing coming to a standstill.

In this book we leverage theory and techniques from fields such as applied physics, communications, and microwave engineering and apply them to the field of high-speed digital design, creating an optimal combination between theory and practical applications. Although some basic material is covered, we assume that readers are well acquainted with basic electromagnetic theory, vector calculus, differential equations, statistics, and transmission-line analysis. In this book we build on the traditional knowledge base and discuss advanced topics ranging from electromagnetic theory for signal integrity to equalization methods that compensate for signal integrity problems with circuitry as required to design modern and future digital systems. Detailed theory is presented in the context of real-life design examples so that it can be applied immediately by practicing engineers, yet provides more than enough technical content to facilitate complete understanding of the concepts.

## Features

- 1. Visual description of theoretical concepts wherever possible, so each chapter includes numerous figures to help reinforce the concepts discussed.

- 2. Rigorous coverage of theory and use of practical examples to demonstrate how to use the theory in practical, real-world applications.

- 3. Summary of the electromagnetic theory concepts required to comprehend signal integrity.

- 4. Rigorous development of transmission-line and crosstalk theory to build a fundamental understanding and then apply the theory to real-world problems.

- 5. Development of physically consistent dielectric and conductor models to account for frequency-dependent properties, surface roughness, and physical anomalies due to manufacturing and environmental effects.

- 6. Description of differential signaling at a practical and a theoretical level.

- 7. Explanation of the mathematical limits of models such as causality, passivity, stability, and reality that must be obeyed to ensure that simulations remain consistent with nature.

- 8. Full description of network theory, including *S*-parameters and frequency-domain analysis.

- 9. Coverage of topics such as nonideal current return paths, tabular modeling, and via resonance.

- 10. Covers the basics of I/O design and channel equalization.

- 11. Methods for modeling and budgeting of timing jitter and noise.

- 12. System analysis techniques for handling large numbers of variables using response surface modeling.

Contemporary signaling systems continue to offer new problems to solve. Engineers who can solve these problems will define the future. This book will equip readers with the necessary practical understanding to contend with contemporary problems in high-speed digital design and with enough theory to see beyond the book to solve problems that the authors have not yet encountered.

## ACKNOWLEDGMENTS

Many people have contributed directly or indirectly to the writing of this book. We have been fortunate to keep the company of excellent engineers, scientists, and peers, whose technical knowledge, wisdom, and mentorship have truly inspired us throughout our careers. Without these contributions, this book would not have been possible. Our gratitude is immeasurable.

Among the direct contributors are: Guy Barnes of Ansoft Corporation, who reviewed our mathematics, provided simulation data for Chapter 10, and provided the graphics for the front cover. Stephen Hall, Sr., Stephen's father, for educating us on how molecules interact with externally applied electric fields and for writing that section in Chapter 6. Paul Huray of the University of South Carolina, who educated us on complicated aspects of electromagnetic theory and acted as a role model for academic excellence. Yun Ling of Intel Corporation, who patiently reviewed our mathematics and politely corrected our mistakes. Kevin Slattery of Intel Corporation, for reviewing Chapter 2 and strongly encouraging us to write the book. Chaitanya Sreerama Burt of Intel Corporation, who both reviewed chapters and double-checked all of our calculations in Chapter 2. Steven Pytel of Ansoft Corporation, who graciously reviewed Chapter 5, correcting errors and making excellent recommendations for improvements. Daniel Hua, for checking results and helping to solve the difficult differential equations. Luis Armenta of Intel Corporation, for reviewing the dielectric models in Chapter 6. Paul Hamilton of Tyco, for reviewing Chapter 6. Gerardo Romo of Intel Corporation, who reviewed Chapters 4 and 12. Michael Mirmak of Intel Corporation and current chair of the IBIS open forum, who reviewed Chapter 11. Richard Allred of Intel Corporation, who reviewed Chapters 13 and 14. Pelle Fornberg and Adam Norman, who reviewed the jitter and peak distortion material in Chapter 13.

Stephen would also like to thank: *Dorothy Hall*, Stephen's mother, for a lifetime of encouragement and for instilling the enthusiasm, discipline, and drive needed not only to become an engineer, but to write this book. *Garrett Hall*, not only for reviewing chapters and double-checking results, but for providing much of the material and motivation for the introduction and for being the most encouraging, devoted, trustworthy, and principled friend that a big brother could ever have.

Howard would like thank *Eric Dibble* of Lockheed-Martin Corporation and *Martin Rausch* of Intel Corporation for supporting his efforts to break into the signal integrity field and for guiding his professional and personal growth. He also thanks *Dr. Ricardo Suarez-Gartner* of Intel Corporation for encouraging him to write the book.

Finally, Stephen dedicates his contributions to this book to his lifelong companion, best friend, wife, and jewel of his life, *Jodi*, with all his love and gratitude, as well as his little girls, *Emily* and *Julia*, who bring him more joy than he could have thought possible.

Howard dedicates his contributions to his beautiful wife, *Lisa*, and sons, *Tyler* and *Nick*, whose support and love provide him the day-to-day happiness that makes each day a gift.

Hillsboro, OR July 2008 STEPHEN H. HALL HOWARD L. HECK

# 1

## **INTRODUCTION: THE IMPORTANCE OF SIGNAL INTEGRITY**

| 1.1  | Computing power: past and future | 1 |

|------|----------------------------------|---|

| 1.2  | The problem                      | 4 |

| 1.3  | The basics                       | 5 |

| 1.4  | A new realm of bus design        | 7 |

| 1.5  | Scope of the book                | 7 |

| 1.6  | Summary                          | 8 |

| Refe | erences                          | 8 |

## 1.1 COMPUTING POWER: PAST AND FUTURE

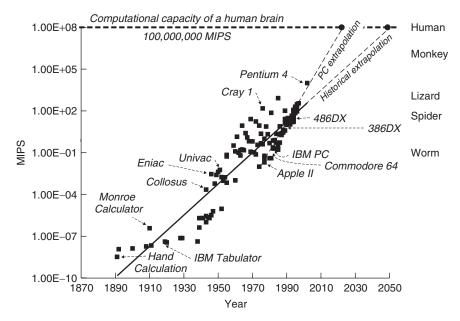

It is estimated that sometime between the years 2025 and 2050, commonplace personal computers will exceed the calculation power of a human brain. Further extrapolation based on historical trends indicates that a single commonplace computer could exceed the computational power of the human race sometime between 2060 and 2100. Are such vast increases in computational power possible in less than 100 years? We cannot say for certain because it is impossible to predict the future. However, hindsight is always 20/20, and if we subscribe to the notion that history tends to repeat itself, we can look at the progress of computational capabilities over the last century to see if historical data support a rate sufficient to achieve such performance. Hans Moravec, a researcher from the Robotics Institute at Carnegie Melon University, estimated that a computer would require 100 million megainstructions per second (MIPS) to mimic sufficiently closely the behavior of a human brain [Moravec, 1998]. Based on the

Advanced Signal Integrity for High-Speed Digital Design, By Stephen H. Hall and Howard L. Heck Copyright © 2009 John Wiley & Sons, Inc.

**Figure 1-1** Historical computational power and extrapolation into the future. (Adapted from Moravec [1998].)

number of neurons, he was also able to compare the current state of computer technology to the estimated computational power of animal brains. These data points outline a particularly interesting way to examine the history of computational power while level-setting computer performance against the brainpower of common animals.

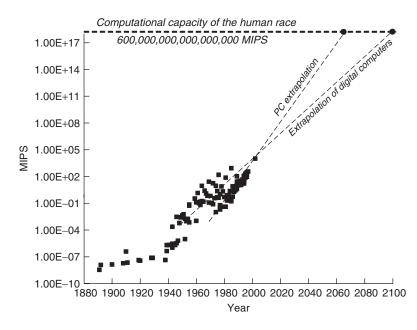

Figure 1-1 plots the computational power for mechanical and electrical computers used over the last 100 years. Some of the more interesting data points are labeled on the plot, ranging from hand calculation (ca. 1/100,000,000 MIPS) to the Pentium 4 processor of 2002 (10,000 MIPS), which is only two orders of magnitude away from the estimated brain power of a monkey (1,000,000 MIPS). As the plot indicates, computers comparable to the human brain could appear as early as the 2020s based on the extrapolation of personal computer (PC) performance over the last three decades. If the historical data for the entire twentieth century are used, the time frame is extended to 2050. The predictions get even more outrageous if we extend the extrapolation to the estimated computational power of all humans presently on Earth (ca. 6 billion), which would require  $6 \times 10^{17}$  MIPS. Such a computer could exist by 2060, as shown in Figure 1-2. The question is: Can the historical pace of development be sustained? Observation of the data indicates that the historical trend shows no sign of slowing. In fact, the rate appears to be increasing.

However, one often encounters articles by knowledgeable people in the computer industry who believe that the trend cannot be sustained and that the decades of exponential growth must stop. In 1998 it was estimated in such an article that

Figure 1-2 Historical computational power and extrapolation into the future.

commonplace printed circuit boards (PCBs) built on an FR4 dielectric could not support bus speeds faster than 300 MHz [Porter, 1998]. Current designs using FR4 substrates exceed that bus speed in commonplace personal computers by almost 10-fold (PCI Express Gen 2 buses run at 5 giga-transfers per second, which has a fundamental frequency of 2.5 GHz). History is filled with "experts" who mispredicted the future:

Heavier-than-air flying machines are impossible.

-Lord Kelvin, British mathematician and physicist, president of the British Royal Society, 1895

Fooling around with alternating current is just a waste of time. Nobody will use it, ever.

-Thomas Edison, American inventor, 1889

Rail travel at high speed is not possible because passengers, unable to breathe, would die of asphyxia.

-Dr Dionysys Larder (1793–1859), professor of natural philosophy and astronomy, University College London

In the mid-1970s, integrated circuits held approximately 10,000 components, which was enough to construct an entire computer with devices as small as 3  $\mu$ m. Experienced engineers worried that semiconductor technology had reached its pinnacle. Three micrometers was barely larger than the wavelength of the light

used to sculpt the chip. Interactions between ever-closer wires were about to ruin the signals. Chips would soon generate so much heat that they would be impossible to cool without a refrigeration unit. The list goes on [Moravec, 1998].

A look at the computer growth graph shows that the industry found solutions to all those problems. Chip progress not only continued—*it sped up*. Technology companies, motivated by the potential of high profits, dedicated tremendous resources to making the "impossible" possible: developing more efficient transistor designs, better heat sinks, new manufacturing processes, and more advanced analysis techniques. History indicates that the rate of performance will continue to grow at exponential rates.

Historically, the mechanism for advancing computation has been to miniaturize components, allowing more devices to fit in and operate in a smaller space, thus producing more performance per unit volume. First, the gears in mechanical calculators shrunk, which allowed them to spin faster. Then the relays in electromechanical machines became smaller, which allowed them to switch faster. Next, the switches in digital machines evolved from shotgun shell–sized vacuum tubes, to pea-sized transistors, to tiny integrated-circuit chips [Moravec, 1998]. Each of these technological advancements came with a price: *New problems that were never before considered arose that needed to be solved*.

How does this relate to signal integrity? The field of signal integrity arose directly from the exponential growth of computing power. A computer system is comprised of many integral components in addition to the processor, such as the memory, cache, and chip set. The interconnections between these parts within a computer system are known collectively as system *buses*. Essentially, a bus is an integrated set of interconnections used to transfer data between different parts of a digital system. Accordingly, to capitalize on the benefits of increased processor power, system buses must also operate at higher data transfer rates. For example, if the memory bus fails to transmit data at a sufficiently fast rate, the processor simply sits idle until data are available. This bottleneck would negate much of the performance gained from a more powerful processor. Subsequently, it is vital that the bus performance scale correspondingly with processor performance.

## **1.2 THE PROBLEM**

The two mechanisms used historically to scale bus design to feed the growing performance of computer processors have been speed and width. *Speed* facilitates higher information transfer rates by sending more bits in a given amount of time. *Width* facilitates more information transfer by sending more bits in parallel. From now on, the rate of information transfer on a bus will be referred to as the *bus bandwidth*.

Increasing the bus speed to overcome bandwidth limitations becomes problematic for many reasons. As bus frequencies increase in speed, the pathways that comprise the bus, called *interconnects*, begin to exhibit high-frequency behavior, which thoroughly puzzles many conventional digital designers. What is required is complete comprehension of the relevant analog techniques and theory commonly used in microwave system and radio designs applied carefully to the digital realm. As the operating frequencies of digital systems increase, these analog effects become more prevalent and severely impede the overall performance if not resolved properly. Furthermore, increased bus speed usually requires more power, which is a precious commodity, especially in mobile designs such as laptops, which rely on battery power.

Increasing the bus width to overcome bandwidth roadblocks is self-limiting. Practical mechanical limitations arise quickly due to increased pin counts on packages, sockets, connectors, and the shortcomings of PCB technology. Furthermore, interactions between closely spaced interconnects lower the signal-to-noise level, making clean data transmission more difficult. Since Moore's law results in computer performance doubling every 18 months, and the bus bandwidth must scale in proportion, doubling the number of signals in the bus to facilitate the required bandwidth provides a solution to the problem that lasts less than two years. Increasing the width of the bus is simply a short-term "band-aid." At some point, faster bus speeds will be required.

The problem is that as bus designs become both wider and faster and form factors shrink to provide more computational power per unit volume, the assumptions used for past designs become outdated and new techniques must be developed. As a result, the field of signal integrity is evolving continuously to encompass new effects that were not relevant to earlier designs. Modern bus designs have become so fast that the designer must calculate the voltage and timing numbers to a resolution as small as a few picoseconds and a few millivolts. This degree of resolution was unheard of in computer designs just a few years ago. Just to put this problem in perspective, the light that is reflected off your nose takes a little over 85 ps to travel to the surface of your eye, which is well over 10 times the required timing resolution of some modern bus designs. This dramatic decrease in bus timing requirements leads to several problems. First, the number of effects that must be accounted for in the design stage increases. This is because effects that were either second order, or ignored completely in previous designs, begin to dominate the performance. Consequently, the total number of variables that must be accounted for increases, which makes the problem more difficult. Furthermore, the new variables are often very difficult or impossible to model using conventional methods. So we have not only many more variables to worry about, but most of the new variables are very difficult to model correctly. Finally, to top it off, the laboratory equipment currently available is often insufficient to resolve these small timing variations, making it difficult or impossible to verify the completed design or to correlate the models to reality.

#### **1.3 THE BASICS**

As the reader undoubtedly knows, the basic idea in digital design is to communicate information with signals representing 1's or 0's. Typically, this involves sending and receiving series of trapezoidal voltage signals in which a high voltage is a 1 and a low voltage is a 0. The conductive paths carrying the digital signals are known as interconnects. The interconnect includes the entire electrical pathway from the chip sending a signal to the chip receiving the signal. This includes the chip packages, connectors, sockets, transmission lines, and vias. A group of interconnects is referred to as a bus. The region of voltage where a digital receiver distinguishes between a high and a low voltage is known as the threshold region. Within this region, the receiver will either switch high or switch low. On the silicon, the actual switching voltages vary with temperature, supply voltage, silicon process, and other variables. From the system designer's point of view, there are usually high- and low-voltage thresholds, known as  $V_{ih}$  and  $V_{il}$ , associated with the receiving silicon, above and below which a high or low value is guaranteed to be received under all conditions. Thus, the designer must guarantee that the system can, under all conditions, deliver high voltages that do not, even briefly, fall below  $V_{ih}$ , and low voltages that remain below  $V_{il}$ , to ensure the integrity of the data.

To maximize the speed of operation of a digital system, the timing uncertainty of a transition through the threshold region must be minimized. This means that the rise or fall time of the digital signal must be as fast as possible. Ideally, an infinitely fast edge rate would be used, although there are many practical problems that prevent this. Realistically, edge rates as fast as 35 ps are encountered in real systems. The reader can use Fourier analysis to verify that the quicker the edge rate, the higher the frequencies that are found in the spectrum of the signal. Herein lies a clue to the difficulty. Every conductor has a frequency-dependent capacitance, inductance, conductance, and resistance. At a high-enough frequency, none of these things are negligible. Thus, a wire is no longer a wire but a distributed, frequency-dependent parasitic element that has delay and a transient impedance profile that can cause distortions and glitches to manifest themselves on the waveform propagating from the driving chip to the receiving chip. The wire is now an element that is coupled to everything around it, including power and ground structures, heat sinks, other traces, and even the wireless network. The signal is not contained in the conductor itself but is, instead, carried in the local electric and magnetic fields around the conductor. The signals on one interconnect will affect, and be effected by, the signals on another. The inductance, capacitance, and resistance of all the structures in the vicinity of the interconnect have vital roles in the simple task of guaranteeing proper signaling transitions with appropriate timing at the receiver.

One of the most difficult aspects of high-speed design is the fact that there are many codependent variables that affect the outcome of a digital design. Some of the variables are controllable, and others force the designer to live with the random variation. One of the difficulties in high-speed design is how to handle the many variables, whether they are controllable or uncontrollable. Often, simplifications can be made by neglecting or assuming values for variables, but this can lead to unknown failures down the road for which it will not be possible after the fact to locate the root cause. As timing becomes more constrained, the simplifications of the past are rapidly dwindling in utility to the modern designer. In this book we also show how to incorporate a large number of variables that would otherwise make the problem intractable. Without a methodology for handling the large number of variables, a design ultimately incorporates some guesswork, no matter how much the designer understands the system physically. The final step in handling all the variables is often the most difficult part and the one most readily ignored by designers. A designer crippled by the inability to handle large numbers of variables will ultimately resort to proving a few "point solutions" instead and hope that they plausibly represent all known conditions. Although such methods are sometimes unavoidable, this can be a dangerous guessing game. Of course, a certain amount of guesswork is always present in design, but the goal of the system designer should be to minimize uncertainty.

## 1.4 A NEW REALM OF BUS DESIGN

Technology has progressed to a point where digital design has entered a new realm, where new design techniques and concepts are required that baffle even the most seasoned digital system designers. The fact is that present and future state-of-the-art digital systems, such as personal computers, cannot be designed without a thorough understanding of the principles outlined in this book. Why hasn't this been a problem before? The answer is that digital designers didn't need to understand these things. But digital circuits are reaching speeds where design will not be possible without an understanding of this subject. Seasoned engineers face the threat of becoming a legacy if they do not adapt to the new design space. This book will help practicing engineers adapt.

From the Monroe calculator to the Pentium, from punch cards to flash memory, from vacuum tubes to integrated circuits, computer performance is increasing at an exponential rate. In this book we address the needs of the contemporary digital designer as he or she encounters the numerous new challenges with modern and future high-speed digital systems and is forced to learn material previously not needed. As the conventional digital designer transitions to faster designs, he or she will indeed experience a completely different view of logic signals at high speeds. This book will help to make sense of the ugly, distorted, and smeared waveforms produced in a high-speed digital system.

## **1.5 SCOPE OF THE BOOK**

This book was written to be an advanced study in signal integrity. Although some basic material is covered, it is assumed that the reader is well acquainted with basic electromagnetic theory, vector calculus, differential equations, statistics, and transmission-line analysis. The book builds on the traditional knowledge base and covers topics required to design present and future digital systems.

## 1.6 SUMMARY

All of this leads to the present situation: There are new problems to solve. Engineers who can solve these problems will define the future. This book will equip readers with the necessary practical understanding to contend with contemporary problems of modern high-speed digital design with enough theory to see beyond this book and solve problems that the authors have not yet encountered.

## ERRATA

Inevitably, some errors will slip past the layers of review. Although they will be remedied in subsequent printings, it is useful to summarize the corrections in one place. The errors, along with the corrections, will be posted at ftp://ftp.wiley.com/public/sci\_tech\_med/high\_speed\_design.

## REFERENCES

Moravec, Hans, 1998, When will computer hardware match the human brain?, *Journal of Evolution and Technology*, vol. 1.

Porter, Chris, 1998, High chip speeds spell end for FR4, *Electronic Times*, Mar. 30.

# 2

## ELECTROMAGNETIC FUNDAMENTALS FOR SIGNAL INTEGRITY

| 2.1 | Maxwell's equations                                                        | 10 |

|-----|----------------------------------------------------------------------------|----|

| 2.2 | Common vector operators                                                    | 13 |

|     | 2.2.1 Vector                                                               | 13 |

|     | 2.2.2 Dot product                                                          | 13 |

|     | 2.2.3 Cross product                                                        | 14 |

|     | 2.2.4 Vector and scalar fields                                             | 15 |

|     | 2.2.5 Flux                                                                 | 15 |

|     | 2.2.6 Gradient                                                             | 18 |

|     | 2.2.7 Divergence                                                           | 18 |

|     | 2.2.8 Curl                                                                 | 20 |

| 2.3 | Wave propagation                                                           | 23 |

|     | 2.3.1 Wave equation                                                        | 23 |

|     | 2.3.2 Relation between $E$ and $H$ and the transverse electromagnetic mode | 25 |

|     | 2.3.3 Time-harmonic fields                                                 | 27 |

|     | 2.3.4 Propagation of time-harmonic plane waves                             | 28 |

| 2.4 | Electrostatics                                                             | 32 |

|     | 2.4.1 Electrostatic scalar potential in terms of an electric field         | 36 |

|     | 2.4.2 Energy in an electric field                                          | 37 |

|     | 2.4.3 Capacitance                                                          | 40 |

|     | 2.4.4 Energy stored in a capacitor                                         | 41 |

| 2.5 | Magnetostatics                                                             | 42 |

|     | 2.5.1 Magnetic vector potential                                            | 46 |

|     | 2.5.2 Inductance                                                           | 48 |

|     | 2.5.3 Energy in a magnetic field                                           | 51 |

| 2.6 | Power flow and the poynting vector                                         | 53 |

|     | 2.6.1 Time-averaged Values                                                 | 56 |

| 2.7 | Reflections of electromagnetic waves                                       | 57 |

Advanced Signal Integrity for High-Speed Digital Design, By Stephen H. Hall and Howard L. Heck Copyright © 2009 John Wiley & Sons, Inc.

2.7.1 Plane wave incident on a perfect conductor572.7.2 Plane wave incident on a lossless dielectric60

References Problems 62 62

Much of signal integrity is based heavily in electromagnetic theory. Various aspects of this theory are found in numerous books on a variety of topics, such as microwaves, electromagnetics, optics, and mathematics. To rely on these books to form a basis of the fundamental understanding of signal integrity would result in a confusing disarray of conflicting assumptions, notations, and conventions. Although it is assumed that readers have a basic understanding of electromagnetics, the presentation of Maxwell's equations and subsequent solutions in the form most often used in signal integrity will minimize confusion and help readers extract the relevance from the haze of mathematical calculation often encountered in generalized electromagnetic textbooks. It is also convenient to summarize, in one place, the underlying physics that forms the basis of succeeding chapters. In this section we present Maxwell's equations and the underlying electromagnetic theory needed for signal integrity. The concepts are used and expanded on in several subsequent chapters. This analysis does not constitute a complete theoretical study; however, it does present the fundamental electromagnetic concepts needed to develop the basis of signal integrity theory. As the book progresses, this material will be built on to describe more advanced concepts as they are applied to real-world examples.

Initially, the most common vector operators are reviewed briefly. This is important because Maxwell's equations will be presented in differential form and a fundamental understanding of the vector operators will allow readers to visualize the behavior of electromagnetic fields. Next, the equations that govern a plane wave propagating in free space are derived directly from Maxwell's equations. Then the concepts of wave propagation, intrinsic impedance, and the speed of light are derived. Next, the theory of electrostatics and magnetostatics is covered to explain the physical meaning of an electric and a magnetic field, the energy they contain, and how they relate to specific circuit elements, such as inductance and capacitance, used in later chapters. Finally, we discuss the power carried by electromagnetic waves and how they react when propagating into different materials, such as metal or other dielectric regions. Other aspects of electromagnetic theory are covered in later chapters, but the basis of that analysis is defined here.

## 2.1 MAXWELL'S EQUATIONS

Electromagnetic theory is described by Maxwell's equations, published originally in 1873. In this section we outline the fundamentals of electromagnetic theory